BCL Molecular Mk II

The Mark II processor was different from the Mk 1 and new features were added.

It didn't go down well! Applications written for the Mk 1 wouldn't work without modifications.

The Mk II was soon dropped and the extra features removed - which is a shame as the new features were quite clever. One was a set of base and limit registers that would be used to detect a task writing to core outside their pre-defined area. The general idea was that it is was a serious issue that one task could 'damage' another or indeed overwrite the operating system. Of course this also stopped each tasks access to zero page and also stopped any inter-process communication. These could have been managed by additional calls into the OS.

A new OS was being written for the Mk 2 to take advantages of the new features.

The Mk II Technical Manual

Ref 202(5.73) Iss. 1

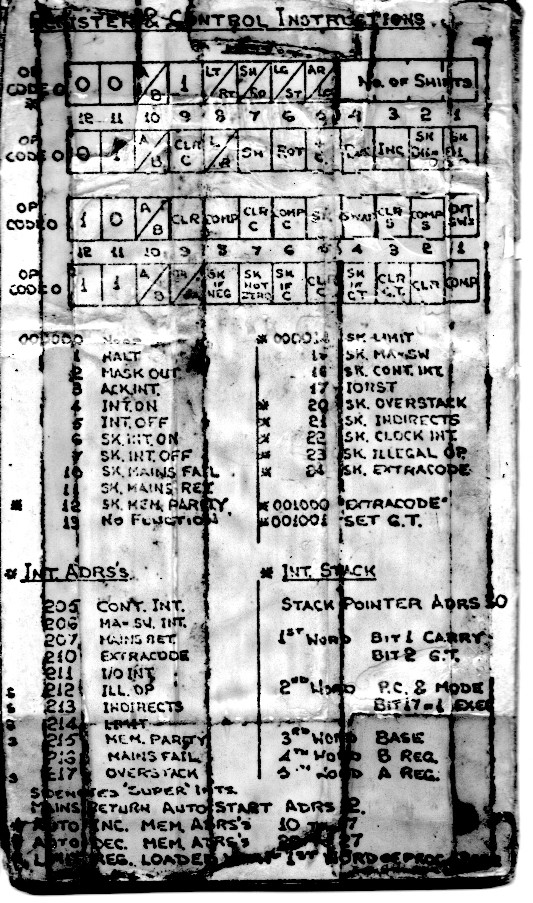

Mk 2 Instruction Card

New functions in Mk 2 processor

There was a hardware interrupt stack counter and a number of associated instructions, (see instruction card alongside 00 00 20 to 00 0024). It also had a variable cycle time so those 2 features meant it was not compatible with the Mk1.

It ran a new operating system, thus none of the existing LOS based applications would run on it which was the killer, there was neither the time nor the money to develop a range of applications.